Bus de datos CAN

El bus de datos CAN ( Controller Area Network ) es un bus de sistema en serie que se usa ampliamente en muchas industrias, especialmente en la industria automotriz .

Ha sido estandarizado con ISO 11898 .

Se aplica un enfoque conocido con el nombre de multiplexación , y que consiste en conectar a un mismo cable (un bus ) un gran número de ordenadores que, por tanto, se comunicarán a su vez. Esta técnica elimina la necesidad de cablear líneas dedicadas para cada información a transmitir (conexión punto a punto). Tan pronto como un sistema (automóvil, avión, barco, red telefónica, etc. ) alcanza un cierto nivel de complejidad, el enfoque punto a punto se vuelve imposible debido a la inmensa cantidad de cableado a instalar y su costo (en masa, materiales, mano de obra, mantenimiento).

La introducción de buses multiplexados (principalmente CAN) en el automóvil tuvo como objetivo reducir la cantidad de cables en los vehículos (entonces había hasta 2 km de cables por automóvil), pero sobre todo permitió la explosión en la cantidad de computadoras y sensores distribuidos. en todo el vehículo, y los servicios correspondientes (reducción de consumos, control de la contaminación , seguridad activa / pasiva , confort, detección de averías, etc. ), reduciendo al mismo tiempo la longitud de los cables.

Histórico

El bus de datos CAN es el resultado de la colaboración entre la Universidad de Karlsruhe y Bosch .

Se utilizó por primera vez en el sector de la automoción , pero actualmente se utiliza en la mayoría de las industrias , como la aeronáutica, a través de protocolos estandarizados basados en CAN.

Fue introducido con Intel en 1985 , pero no fue estandarizado por ISO hasta principios de la década de 1991.

En 1992, varias empresas se unieron para crear CAN in Automation, una asociación que tiene como objetivo promover CAN.

Se ha lanzado un primer desarrollo llamado FD para "Flexibel Data rate".

Se está desarrollando una segunda evolución de Bosch , denominada "XL".

Capa fisica

Hay dos estándares para la capa física:

- ISO 11898-2 (2003): CAN “alta velocidad” (hasta 1 Mbit / s );

- ISO 11898-3 (2006): CAN “baja velocidad, tolerante a fallos” (hasta 125 kbit / s ).

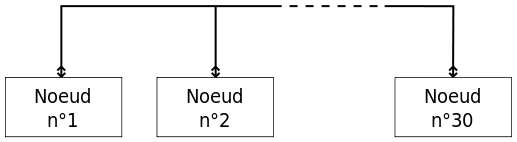

Topología

CAN es un bus de datos en serie bidireccional semidúplex en la industria automotriz, pero se utiliza unidireccional ( simplex ) en aeronáutica para lograr un comportamiento determinista .

Cada dispositivo conectado, llamado "nodo", puede comunicarse con todos los demás.

Para un bus de datos CAN de “baja velocidad”, el número de nodos está limitado a 20. Para un bus de datos CAN de “alta velocidad”, está limitado a 30.

Apoyo

Cada nodo está conectado al bus mediante un par trenzado (blindado o no) .

Los dos extremos del bus deben estar conectados mediante resistencias de 120 Ω ± 10% (tolerancia entre 108 Ω y 132 Ω).

El acceso al bus de datos CAN sigue la técnica CSMA / CR (escuchar cada estación antes de hablar pero no hablar, resolución de colisiones por prioridad).

La longitud máxima del bus está determinada por la velocidad utilizada:

| Velocidad ( kbit / s ) |

Longitud ( m ) |

|---|---|

| 1000 | 30 |

| 800 | 50 |

| 500 | 100 |

| 250 | 250 |

| 125 | 500 |

| 62,5 | 1000 |

| 20 | 2500 |

| 10 | 5,000 |

Codificación de bits

La codificación utilizada es del tipo NRZ (sin retorno a 0) :

Estados lógicos y niveles eléctricos

Los nodos están cableados en el bus según el principio de "cableado OR" desde el punto de vista eléctrico ("cableado Y" desde el punto de vista lógico), lo que significa que en caso de transmisión simultánea desde dos nodos, el valor 0 sobrescribe el valor 1.

Entonces decimos:

- que el estado lógico "0" es el estado "dominante";

- que el estado lógico "1" es el estado "recesivo".

Los estados lógicos y los niveles eléctricos utilizados entre las dos líneas del par diferencial para el CAN de baja velocidad son los siguientes:

| Estado lógico | V CANH-GND | V CANL-GND | V CANH-CANL |

|---|---|---|---|

| Recesivo o "1" | 1,75 V | 3,25 V | −1,5 V |

| Dominante o "0" | 4 V | 1 V | 3 V |

Los estados lógicos y los niveles eléctricos utilizados entre las dos líneas del par diferencial para el ADC de alta velocidad son los siguientes:

| Estado lógico | V CANH-GND | V CANL-GND | V CANH-CANL |

|---|---|---|---|

| Recesivo o "1" | 2,5 V | 2,5 V | 0 hasta 0,5 V |

| Dominante o "0" | 3,5 V | 1,5 V | de 0,9 a 2 V |

Tiempo y velocidad

La duración de un bit se denomina "tiempo de bit nominal".

Cada bit se compone de varios segmentos sincronizados por el reloj interno de cada nodo:

- segmento de sincronización;

- segmento de propagación;

- tampón de segmento de fase n o 1;

- segmento de búfer de fase n o 2.

El "tiempo cuántico" es la unidad de tiempo construida a partir del período del oscilador interno de cada nodo.

La frecuencia del bus es como máximo de 1 MHz y las de los osciladores de varios MHz, el “Time Quantum” generalmente vale varios períodos de reloj (entre 1 y 32 veces).

La duración de cada segmento es la siguiente:

| Segmento | Duración en "Time Quantum" |

|---|---|

| Sincronización | 1 |

| Propagar | de 1 a 8 |

| Fase tampón n o 1 | de 1 a 8 |

| Fase tampón n o 2 | de 2 a 8 |

Por tanto, la duración de un bit puede variar de 5 a 25 "Time Quantum".

Cuanto mayor sea la frecuencia del reloj interno del nodo, más corta puede ser la duración del “Time Quantum”, más contarán los últimos tres segmentos “Time Quantum” y mejor será la precisión de sincronización.

Segmento de sincronizaciónEl segmento de sincronización se utiliza para sincronizar los diferentes nodos.

La transición de 0 a 1 o de 1 a 0, realizada para el nodo emisor, debe tener lugar en este segmento. Si para un nodo receptor esta transición no se produce en este mismo segmento es porque está desincronizado. Este es un error de fase.

Gracias al bit de transparencia, esta verificación se puede realizar al menos cada 5 bits (para los primeros campos de la trama en la que se utiliza).

Segmento de propagaciónEl segmento de propagación se utiliza para compensar los fenómenos de propagación en el bus.

Segmentos de faseLos segmentos de fase se utilizan para compensar los errores de fase detectados durante las transiciones.

La duración de estos segmentos puede variar en caso de resincronización.

Punto de muestreoEl punto de muestreo o “Punto de muestreo” es el instante en el que se lee el valor del bit en el bus. Esto ocurre entre los dos segmentos de fase.

SincronizaciónHay dos tipos de sincronización:

- sincronización dura que consiste en resincronizar bruscamente tan pronto como se detecta una transición en el segmento de sincronización, en particular durante el SOF (Start Of Frame) de una nueva trama;

- resincronización que consiste en alargar el segmento de tampón de fase n o 1 o reduciendo el segmento de tampón de fase n o 2, que tiene dos efectos:

- mover el punto de muestreo,

- disminuir o aumentar la duración del bit y así mejorar la sincronización del siguiente bit.

Conector

El pinout en el bus de datos CAN está estandarizado y usa un conector DE-9 :

| Broche | Descripción |

|---|---|

| 1 | (Reserva) |

| 2 | PUEDO |

| 3 | Masa |

| 4 | (Reserva) |

| 5 | Blindaje (opcional) |

| 6 | Masa |

| 7 | CANH |

| 8 | (Reserva) |

| 9 | Fuente de alimentación externa (opcional) |

Capa de enlace de datos

También hay dos estándares para la capa de enlace de datos:

- ISO 11898 parte A → CAN 2.0A “formato de trama estándar” (identificación de 11 bits);

- ISO 11898 parte B → CAN 2.0B “formato de trama extendido” (identificación de 29 bits).

Hay varios tipos de marcos:

- marco de datos;

- marco de consulta;

- marco de error;

- marco de sobrecarga.

Entre dos tramas, los transmisores deben observar una pausa (período entre tramas) equivalente a la duración de tres bits durante los cuales el bus se mantiene en estado recesivo.

Marco de datos

El marco de datos se utiliza para enviar información a otros nodos.

Un marco de datos consta de siete campos diferentes:

- el inicio de la trama o SOF (Start Of Frame) materializado por 1 bit dominante;

- el campo de arbitraje (identificador) compuesto por 12 o 32 bits;

- el campo de comando (o control) compuesto por 6 bits;

- el campo de datos compuesto por 0 a 64 bits (0 a 8 bytes);

- el campo CRC compuesto por 16 bits;

- el campo de acuse de recibo compuesto por 2 bits;

- el final de la trama o EOF (End of Frame) materializado por 7 bits recesivos.

Orden de transmisión de bits

Orden de transmisión de bits

Los campos se transmiten en orden de SOF a EOF.

En cada campo de la trama, los bits se transmiten del más fuerte al más débil.

Campo de arbitrajeEl campo de arbitraje está compuesto por 11 bits de identificación para CAN 2.0A y 29 bits para CAN 2.0B seguidos por el bit RTR (Solicitud de transmisión remota) que es dominante. Este campo sirve como identificador de los datos transportados en el campo de datos.

Los 11 bits de CAN 2.0A permiten 2 11 = 2048 combinaciones.

Los 29 bits de CAN 2.0B permiten 2 29 = 536 870 912 combinaciones.

Campo de comandoEl campo de control se compone de seis bits.

El bit más significativo se utiliza para diferenciar el tipo de trama:

- en el caso de una trama estándar (en 11 bits), el bit más significativo es el dominante;

- en el caso de una trama extendida (en 29 bits), el bit más significativo es recesivo.

El siguiente bit no se usa.

Los cuatro bits menos significativos llamados DLC (Código de longitud de datos) representan el número de bytes del campo de datos integrado (PAYLOAD).

Este número de bytes puede variar de 0 a 8, o nueve valores almacenados con los cuatro bits del campo DLC. Por tanto, no se utilizarían valores de DLC superiores a 9 (de 9 a 15).

Campo de datosEl campo de datos puede variar de 0 a 8 bytes.

En el caso de un marco de solicitud, el campo de datos está vacío.

Campo CRCEl campo se compone de quince bits de CRC (Cyclic Redundancy Check) y de un denominado bit delimitador (“CRC delimiter”) que siempre es recesivo.

Le CRC est calculé à partir de l'ensemble des champs transmis jusque-là (c'est-à-dire le SOF, le champ d'arbitrage, le champ de commande et le champ de données ; les bits de transparence ne sont pas tener en cuenta). El conjunto constituye el polinomio f ( x ).

El algoritmo consiste en primer lugar en multiplicar f ( x ) por 2 15 .

Luego, el polinomio f ( x ) se divide (módulo 2) por el polinomio g ( x ) = x 15 + x 14 + x 10 + x 8 + x 7 + x 4 + x 3 + x 0 .

Una vez realizadas las sucesivas divisiones, el resto constituye la secuencia CRC.

La distancia de Hamming del algoritmo utilizado es 6, lo que significa que se pueden detectar un máximo de cinco errores.

Gracias a este sistema de detección, la tasa de error registrada es muy baja (menos de 4,6 × 10 −11 ). Además, la red puede diferenciar los errores puntuales de los errores redundantes. Por lo tanto, cualquier dispositivo defectuoso puede desconectarse de la red para limitar las perturbaciones. A continuación, la red entra en modo "degradado".

Campo de acuse de reciboEl campo está compuesto por un bit de acuse de recibo ACK (ACKnowledge) y un bit delimitador (“ACKnowledge delimiter”) que es siempre recesivo.

Todos los receptores que han recibido el mensaje con éxito deben reconocerlo transmitiendo un bit dominante durante la duración del bit ACK, lo que permite al nodo emisor saber que al menos uno de los nodos receptores ha recibido el mensaje.

Si un nodo receptor no recibió el mensaje o lo recibió incorrectamente, no puede usar este mecanismo para señalar el error, ya que una estación receptora solo necesita enviar un bit dominante para enmascarar todos los bits recesivos. Para señalar el mal funcionamiento, debe enviar un cuadro de error.

Marco de solicitud

El marco de solicitud se utiliza para solicitar datos de otro nodo. Es similar al marco de datos excepto:

- el campo de datos está vacío;

- el bit RTR del campo de arbitraje es recesivo;

- los cuatro bits DLC del campo de comando corresponden al número de bytes esperados en la respuesta.

Nótese que el hecho de que el bit RTR sea recesivo en el caso de una trama de solicitud significa que si una trama de datos se envía simultáneamente con el mismo campo de arbitraje, es la trama de datos la que tiene prioridad.

Bit de transparencia

Para asegurar la transmisión de mensajes, se utiliza el método de " relleno de bits ".

Consiste, en el caso de que se hayan enviado cinco bits de la misma polaridad seguidos, agregar un bit de polaridad opuesta a la secuencia, para romper cadenas excesivamente grandes de bits idénticos. Este método solo se aplica a los campos SOF, arbitraje, comando, datos y CRC (delimitador excluido).

Por ejemplo, "1111 1110" se convertirá en "1111 1011 0".

Prioridad de transmisión

¿Qué sucede si varios nodos intentan transmitir simultáneamente?

Existe un procedimiento de acceso al bus al que debe someterse cada nodo:

- al transmitir un bit, el nodo debe escuchar el bus. Es decir, después de haber enviado un bit, lee el bus y comprueba que el bit leído corresponde al transmitido;

- si hay una diferencia (necesariamente en un bit recesivo), es porque otro nodo la ha sobrescrito con un bit dominante;

- el nodo debe entonces interrumpir su transmisión, monitorear el bus para esperar el final de la transmisión y luego intentar nuevamente enviar su mensaje.

Así se consigue una prioridad gracias al campo del arbitraje.

Cuanto más pequeño es, más contiene bits de orden superior 0 (dominante), más prioridad tendrá.

Esta fase de priorización o arbitraje finaliza en el bit RTR.

Marco de error

Tan pronto como se detecta un error, el nodo no espera el final de la trama incriminada, envía inmediatamente una trama de error para señalar un problema en la transmisión.

Un marco de error consta de dos campos diferentes:

- la bandera de error de seis bits;

- el delimitador consta de ocho bits recesivos.

El marco de error puede ser:

- "Activo" si la bandera de error consta de seis bits dominantes;

- "Pasivo" si el indicador de error consta de seis bits recesivos.

Los nodos detectan una serie de errores.

Error de bitCada vez que un nodo emite un bit en el bus, vuelve a leer el bus y debe encontrar el bit que escribió. Si al enviar un bit recesivo vuelve a leer un bit dominante, ha sido alterado.

Este mecanismo es idéntico al que permite la priorización, por lo que no debe tenerse en cuenta en el ámbito del arbitraje.

Lo mismo ocurre con el campo de acuse de recibo, si el bit recesivo enviado por el nodo emisor se vuelve dominante, es simplemente que uno o más nodos receptores han confirmado la recepción correcta de la trama, por lo que no es un error.

Error de cosasSi se leen seis bits consecutivos de la misma polaridad en el bus, el mecanismo de bits de transparencia no se ha respetado o se ha alterado un bit.

Error de CRCSi el valor CRC calculado por el nodo receptor es diferente del CRC codificado en la trama por el nodo emisor, la trama se ha corrompido.

Delimitador de CRCSi el bit "delimitador CRC" leído por los nodos receptores no es recesivo, el bit ha sido alterado.

Error de ACKnowledgeSi el bit ACK recesivo enviado por el nodo emisor no ha sido anulado por un bit dominante, entonces ningún nodo receptor lo ha recibido.

AC Delimitación de conocimientosSi el bit "ACKnowledge delimiter" leído por los nodos receptores no es recesivo, el bit ha sido alterado.

Error de recuperaciónPor construcción, la trama de error rompe la regla del relleno de bits ya que, pase lo que pase, los seis bits de la bandera de error son idénticos.

Cuando un nodo envía una trama de error, todos los demás nodos detectan un error de tipo "Stuff error" y también comienzan a enviar una trama de error.

En el caso de tramas de error activas, el número de bits dominantes en una fila no debe exceder los doce bits. Más allá de eso, los nodos que no han enviado su marco de error no deben hacerlo.

El último nodo en enviar proporciona el delimitador (ocho bits recesivos) y finaliza la cacofonía.

El nodo que envió la trama incriminada luego retira su oportunidad.

Y así sucesivamente, hasta que la trama pasa o uno de sus contadores de errores hace que el nodo cambie el modo de error.

Contadores de erroresCada nodo tiene dos contadores de errores:

- un contador de errores de transmisión o “Contador de errores de transmisión” (TEC);

- un contador de errores de recepción o “Contador de errores de recepción” (REC).

El contador de errores de transmisión de un nodo en modo transmisor es:

- incrementado en 8:

- si el nodo envía una bandera de error excepto:

- en caso de "ACKnowledge error" y está en modo de error pasivo,

- en el caso de un "error material" durante el período de arbitraje,

- si el nodo recibe siete bits dominantes consecutivos después de una bandera de error o una bandera de sobrecarga;

- si el nodo envía una bandera de error excepto:

- decrementado en 1 si la transmisión del nodo es exitosa.

El contador de errores de recepción de un nodo en modo receptor es:

- incrementado en 1 si el nodo detecta un error de recepción, excepto en el caso de “Bit error” durante una bandera de error o una bandera de sobrecarga;

- incrementado en 8:

- si el nodo recibe un bit dominante justo después de una bandera de error,

- si el nodo detecta un "error de bit" durante una bandera de error o una bandera de sobrecarga,

- si el nodo recibe 7 bits dominantes consecutivos después de una bandera de error o una bandera de sobrecarga;

- decrementado en 1 si es menor que 127 y el nodo recibe una trama libre de errores;

- reducido entre 119 y 127, si es mayor que 127 y el nodo recibe una trama libre de errores.

Dependiendo de los contadores de errores, el nodo cambia el modo de error. Hay tres:

- modo de error activo: en el caso de que TEC y REC sean inferiores a 127. El nodo envía entonces tramas de error activas;

- modo de error pasivo: en el caso de que TEC o REC sea mayor / igual a 128 y menor que 255. El nodo envía entonces tramas de error pasivo;

- Modo “Bus Off”: en el caso de que TEC o REC sea superior a 255. El nodo se desconecta del bus. Para salir de este modo, el nodo debe recibir 128 tramas recesivas de 11 bits.

Marco de sobrecarga

El marco de sobrecarga se puede utilizar en dos casos:

- cuando el nodo solicita un retraso con la recepción de una nueva trama;

- cuando el nodo detecta un bit dominante durante un período entre tramas (tres bits recesivos entre tramas).

Una trama de sobrecarga consta de dos campos diferentes:

- la bandera de sobrecarga compuesta por seis bits dominantes;

- el delimitador consta de ocho bits recesivos.

La trama de sobrecarga es similar a una trama de error activa.

Cuando un nodo transmite una trama de sobrecarga para solicitar un retardo (condición n o 1), sobrescribe los tres bits recesivos del período entre tramas, los nodos restantes detectan sobrecarga y ellos mismos emiten sobrecarga de tramas (condición n o 2).

Al igual que con las tramas de error activas, el número de bits dominantes en una fila no debe exceder los doce bits. Más allá de eso, los nodos que no han enviado su marco de sobrecarga no deben hacerlo.

El último nodo en enviar proporciona el delimitador (ocho bits recesivos) y finaliza la cacofonía.

Capa de aplicación

Se han definido varias capas de aplicación en el estándar CAN:

- CANopen ;

- DeviceNet ;

- SAE J1939 ;

- ISO11783 (ISOBUS) ;

- NMEA2000 ;

- CANaerospace ;

- MilCAN ;

- SocketCAN ;

- FlexCAN ;

- CALIFORNIA;

- SDS;

- CAN Reino.

Bibliografía

- Dominique Paret, Le bus Can: Descripción, de la teoría a la práctica , Dunod,2009, 277 p. ( ISBN 978-2-10-004764-2 )

- (en) Wolfhard Lawrenz, Ingeniería de sistemas Can: de la teoría a las aplicaciones prácticas , Springer,2007, 468 p. ( ISBN 978-0-387-94939-0 )Libro en inglés escrito por el director de proyectos de red CAN de Bosch al crear el protocolo.

Notas y referencias

- http://ww1.microchip.com/downloads/en/AppNotes/00754.pdf

- https://www.can-cia.org/fileadmin/resources/documents/proceedings/2003_fellmeth.pdf

- https://can-newsletter.org/engineering/applications/160322_25th-anniversary-mercedes-w140-first-car-with-can/

- https://www.can-cia.org/can-knowledge/can/can-history/

- https://www.enib.fr/~kerhoas/can.html

- " The CAN bus " , en igm.univ-mlv.fr (consultado el 24 de octubre de 2018 )

- ISO 11898-2: 2003 , en iso.org , 30 de julio de 2014 (consultado el 28 de diciembre de 2015)

Ver también

Artículos relacionados

- Bus de campo

- I2C

- Autobús LIN

- FlexRay

- LA MAYORÍA

- OSEK / VDX

enlaces externos

- Sitio web de CAN in Automation

- P. Kadionik, cursos sobre CANbus de ENSEIRB [PDF]

- (in) Discusión independiente de la plataforma CANLIST

- (es) Diferentes interfaces CAN

- (in) 1 Dr. estudio determinismo bus CAN

- (en) 2 nd estudio sobre el determinismo del bus CAN

- CAN bus en el automóvil

- Tutorial de protocolo CAN